В ходе своего последнего отчета о прибылях за первый квартал TSMC объявила, что ее технологический процесс FinFET с нормами 7 нанометров введен в массовое производство (HVM), что означает, что мы можем увидеть потребительские устройства с этим процессом уже во второй половине этого года.

Предыдущие отчеты указывали на то, что TSMC ожидает получить исключительную ответственность за производство предстоящего чипа Apple A12 и его вариантов, которые, как ожидается, дебютируют в новых продуктах iPhone и iPad начиная с этой осени. Ожидается, что 7-нанометровый процесс (обозначаемый как CLN7FF, 7FF или просто N7) обеспечит примерно 40-процентное преимущество по энергопотреблению и площади по сравнению с 10-нанометровым процессом FinFET от TSMC, используемым в процессорах Apple A11.

Кроме того, как сообщает EETimes, TSMC предоставила информацию о своей дорожной карте технологий как для своих кремниевых процессов, так и для технологий корпусирования устройств. Считается, что TSMC отвоевала эксклюзивное производство процессоров Apple у двойного поставщика Samsung благодаря своим достижениям в области корпусирования на уровне пластины (wafer-level packaging). (На тот момент также в основном осталось незамеченным представление TSMC конденсаторов с боковым расположением, прикрепленных непосредственно к подложке.)

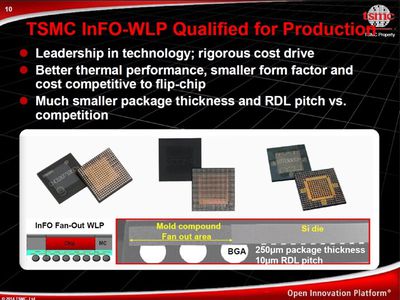

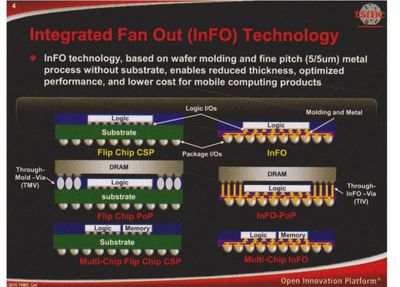

Опираясь на лидерство в области корпусирования, достигнутое благодаря предложениям по корпусированию InFO, TSMC теперь анонсировала шесть новых типов корпусирования, ориентированных на различные устройства и приложения.

Техника InFO получает четыре «родственника». Info-MS, для подложки памяти, упаковывает SoC и HBM на подложке размером с одну ретикулу (1x) с уровнем перераспределения 2 x 2 микрона и будет сертифицирована в сентябре.

InFO-oS имеет обратную сторону RDL (redistribution layer) с более точным соответствием DRAM и готова сейчас. Вариант с многоуровневым стекированием под названием MUST помещает один или два чипа поверх другого, большего чипа, соединенного через интерпозер у основания стека.

Наконец, InFO-AIP означает «антенна в корпусе» (antenna-in-package), обеспечивая на 10% меньший форм-фактор и на 40% более высокий коэффициент усиления. Он ориентирован на такие конструкции, как фронтальные модули для 5G-модемов.

Но это еще не все. TSMC представила два совершенно новых варианта корпусирования. Корпус «пластина на пластине» (wafer-on-wafer, WoW) напрямую соединяет до трех кристаллов. Он был выпущен на прошлой неделе, но пользователям необходимо убедиться, что их EDA-потоки поддерживают технику соединения. Поддержка EMI будет добавлена в июне.

Наконец, foundry примерно описала нечто, что она назвала «системы на интегрированных чипах» (system-on-integrated-chips, SoICs), используя соединения менее 10 микрон для связи двух кристаллов, но детали этой техники, которая будет выпущена в следующем году, пока еще скудны. Она ориентирована на приложения от мобильных устройств до высокопроизводительных вычислений и может соединять кристаллы, изготовленные по разным техпроцессам, что предполагает, что это может быть форма «система в корпусе» (system-in-package).

Объявление этих технологий корпусирования важно, поскольку они позволят реализовать различные структуры корпусов и соединений для SoC Apple, причем непосредственное преимущество заключается в новых интерфейсах для памяти в корпусе. В то время как InFO предлагает преимущества по высоте, производительности и тепловым характеристикам для Apple, им все еще необходимо соединяться с ОЗУ, расположенной поверх процессора приложений, с помощью проводных соединений в конфигурации «корпус на корпусе» (package-on-package).

Этот интерфейс создает тепловые проблемы и ограничивает ширину и скорость шины памяти из-за типа соединений. Индустрия интегральных схем видела немало усилий в области новых технологий памяти, таких как High Bandwidth Memory (HBM), но эта технология в основном ограничивалась графическими процессорами, предназначенными для научных, исследовательских и энтузиастских применений, из-за высокой стоимости и низкого выхода годных материалов кремниевых интерпозеров, которые обеспечивают соединения от чипа к памяти. Тот факт, что TSMC представила вариант InFO, напрямую нацеленный на это решение, предвещает его более широкое внедрение в индустрии в различных продуктах.

Процесс InFO-oS представляет гораздо больший краткосрочный интерес для производителей мобильных устройств, таких как Apple, где ширина шины памяти будет значительно ниже, но пропускная способность на вывод будет намного выше, как видно на примере LPDDR4. Согласно отчету TSMC, часть «oS» в этой технологии относится к «on-substrate» (на подложке), где будет происходить разделение кристаллов.

Это, казалось бы, позволяет реализовать 2.5D-решение, где кристалл памяти располагается рядом с кристаллом процессора, а не подвешивается над ним через компаунд, как в исходном корпусировании InFO-WLP, что обеспечивает более высокую плотность соединений. Однако сохранение слоя перераспределения означает, что компаунд все равно должен присутствовать, поэтому более полное техническое раскрытие информации может помочь устранить некоторую двусмысленность этого названия. Хотя это и устранило бы стекирование кристаллов, это увеличило бы общую площадь упакованного решения, что по-прежнему было бы проблемой для компактного мобильного корпуса.

Хотя Apple в конечном итоге может перейти на решение HBM, которое обеспечивает гораздо большую пропускную способность памяти при более низком энергопотреблении, анонс wafer-on-wafer (WoW) является реальным шагом к истинным 3D-интегрированным схемам, где в конечном итоге кристаллы будут уложены непосредственно друг на друга и соединены через переходные отверстия, расположенные непосредственно в кристалле ИС.

Инновация для TSMC здесь будет заключаться именно в том, как она упаковывает эти кристаллы вместе, как выглядят интерфейсы, а также какие типы слоев перераспределения (RDL) они предлагают. Хотя InFO-AIP напрямую не применим к линейке процессоров Apple, это также важное развитие, поскольку радиочастотные (RF) фронтальные модули стоят на пороге еще одного порядка сложности с их внедрением гораздо более широких полос частот, необходимых для стандартов 5G.

Помимо 7-нанометрового процесса, TSMC также поделилась своими планами относительно последующих процессов foundry — 7 нм+ и 5 нм. 7 нм+ будет первым процессом TSMC, использующим экстремальную ультрафиолетовую (EUV) литографию, которая упростит процесс маскирования, устранив необходимость в многократном шаблонировании во многих областях для формирования более мелких структур.

За 7 нм+ последует 5 нм, который войдет в рисковое производство к концу следующего года, если текущие сроки сохранятся, что означает, что массовое производство будет осуществляться примерно в 2020 году, хотя, вероятно, слишком поздно для запуска продукта осенью 2020 года, даже при самых оптимистичных сроках. Хотя EUV долгожданна и решит многие проблемы в отрасли, она приносит с собой целый ряд собственных проблем и не приведет к огромным скачкам производительности в последующих процессах, а также не обеспечит более плавные переходы между процессами, поскольку 5 нм уже представляет свои собственные проблемы с EUV.

Процесс обеспечивает на 35% большую скорость или потребляет на 65% меньше энергии и обеспечивает 3-кратное увеличение плотности маршрутизированных вентилей. Напротив, процесс N7+ с EUV обеспечит только на 20% большую плотность, на 10% меньшее энергопотребление и, по-видимому, никакого увеличения скорости — и эти усовершенствования требуют использования новых стандартных ячеек.

Тем не менее, вышеупомянутые новости обнадеживают, поскольку Apple должна иметь возможность пользоваться преимуществами нового технологического процесса как минимум два из следующих трех лет. Это даст толчок по мере замедления развития архитектуры ее процессоров, а появление новых методов корпусирования позволит Apple преодолеть ограничения по пропускной способности и тепловыделению способами, которые раньше были просто невозможны.

TSMC также дала надежду на будущее, обрисовав картину за пределами 5 нм в общих чертах с планами по внедрению новых транзисторных топологий, таких как кремниевые нанопроволоки, и переходу от кремния в качестве основного полупроводникового материала к материалам, которые в конечном итоге предлагают более высокую подвижность носителей (электронов и дырок).

TSMC также подробно описала способы улучшения проводимости и снижения паразитных явлений, связанных с соединениями, присутствующими в кремниевом кристалле. В конечном итоге эти соединения часто определяют, насколько быстро транзисторы могут переключаться из-за эффективной нагрузки на линии, и это проблема на всех этапах — от кристалла до корпуса и до печатной платы. TSMC, по-видимому, усердно ищет различные решения для своих клиентов по двум из этих направлений, а ее упаковочные решения все больше переносят эти компоненты печатной платы непосредственно в корпус устройства для борьбы с третьим элементом.