Постоянное стремление Apple к повышению производительности, увеличению времени автономной работы и созданию более тонких корпусов, по-видимому, стимулирует ее исследования в области передовых технологий упаковки чипов. Так называемые методы упаковки «2.5D» и «3D» могут обеспечить значительные преимущества во всех этих областях за счет увеличения пропускной способности памяти, снижения энергопотребления и освобождения места для аккумуляторов большей емкости.

Apple является активным пользователем новых методов упаковки устройств, в основном благодаря инновациям в области интегрированного внешнего монтажа (InFO), предоставляемым партнером-литейщиком TSMC. Успех TSMC подтолкнул ее к дальнейшему развитию и диверсификации предложений по упаковке, и TSMC стала лидером отрасли в технологиях упаковки.

Хотя версии упаковки InFO от TSMC привели к повышению производительности устройств Apple, таким как лучшее управление тепловым режимом и улучшенная высота корпуса, они в значительной степени не способствовали повышению электрических характеристик. Это должно измениться с будущими методами упаковки, и уже наблюдается в некоторых продуктах, которые используют интерпозеры для высокоплотных межсоединений с памятью на кристалле, такой как память с высокой пропускной способностью (HBM).

Основным кандидатом на включение в такой корпус будет память, соответствующая стандартам Wide I/O, описанным JEDEC, и упомянутым по имени в нескольких патентах. Эта память превосходит LPDDR4 за счет увеличения количества каналов и снижения скорости передачи данных на канал, тем самым увеличивая общую пропускную способность, но снижая энергию, необходимую на бит.

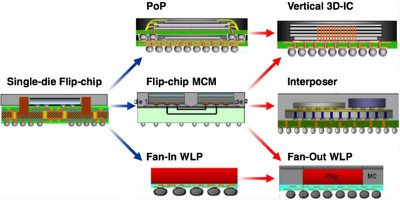

Однако интерпозеры создают несколько проблем для мобильных устройств. Важно отметить, что они добавляют еще один вертикальный элемент к корпусу, увеличивая общую высоту. Интерпозеры также должны изготавливаться на кремниевых пластинах, как и активные ИС, причем их размеры определяются площадью всех устройств, которые необходимо включить в корпус. Эти решения обычно называют «2.5D» из-за того, что некоторые компоненты расположены в боковом направлении относительно друг друга, а не являются истинным стекированием чипов.

Вместо того чтобы использовать интерпозеры для своих продуктов в качестве следующего шага в передовой упаковке, направление фокуса Apple, согласно нескольким патентным заявкам [1][2][3][4], похоже, заключается в истинных «3D» технологиях, когда логические кристаллы, такие как память, размещаются непосредственно поверх активной SoC. Кроме того, патентная заявка от TSMC, по-видимому, предполагает определенный уровень координации между Apple и TSMC в этих усилиях.

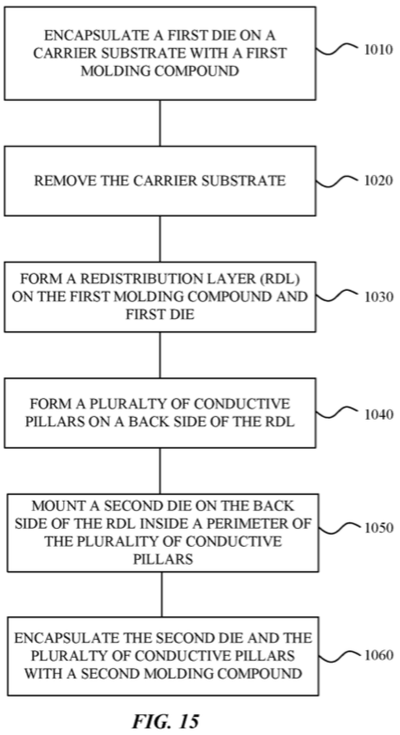

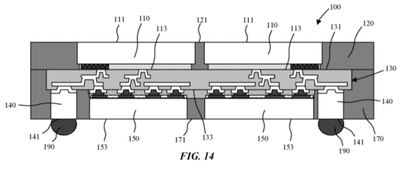

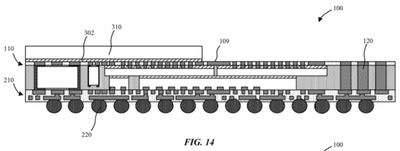

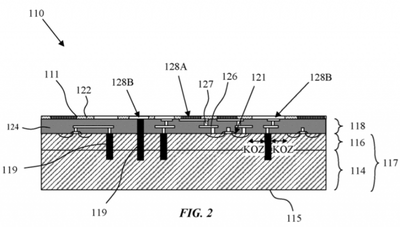

Процесс имеет сходство с существующими технологиями InFO, поскольку оба они включают слой перераспределения (RDL), где контакты на логическом кристалле маршрутизируются внутри компаунда с помощью переходных отверстий непосредственно в компаунде. Отличие 3D-процесса заключается в том, что теперь RDL находится на обеих сторонах кристалла, что требует использования сквозных кремниевых переходных отверстий (TSV) непосредственно в логическом кристалле для обеспечения межсоединений с верхней частью кристалла. Ключевой особенностью этих RDL-слоев является возможность создания более тонких шагов межсоединений, чем доступные на подложке или интерпозере.

Последующие кристаллы затем могут быть прикреплены к компаунду, соединяясь с переходными отверстиями и RDL, расположенными на предыдущем этапе. Этот этап может выполняться многократно, при условии, что каждый собранный компонент имеет TSV для следующего уровня интеграции, и это уже наблюдается в HBM, которая позволяет стекировать до восьми кристаллов DRAM.

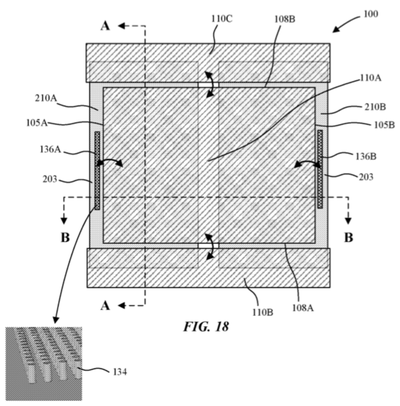

Тем не менее, этот подход имеет много технических проблем, которые препятствовали его коммерциализации. TSV дороги во внедрении и являются серьезным фактором снижения выхода ИС. Электрическая изоляция от излучаемой энергии соседних компонентов также может быть проблемой, особенно при интеграции РЧ и аналоговых компонентов в корпус с другими компонентами, которые ранее были разделены пространством и экранированием ЭМП. Apple описывает методы интеграции экранирования непосредственно в корпус для смягчения этой проблемы.

Этот подход также создает тепловые проблемы, поскольку активные кристаллы становятся настолько тесно связанными в средах с плохой теплопроводностью и общими тепловыми путями. Эти проблемы распространяются не только на нормальное использование устройства, но и на интеграцию корпуса и любые этапы пайки оплавлением. Тепловые напряжения могут вызывать коробление компонентов корпуса из-за различных коэффициентов теплового расширения (CTE) материалов, используемых в корпусе. Это коробление может привести к разрыву или разделению контактов, что приведет к отказу устройства.

Использование несущей подложки в технологическом процессе смягчает некоторые тепловые проблемы. Прямая интеграция радиаторов в упаковку устройств также рассматривается на различных уровнях сборки корпуса, таким образом, что кристаллы с более высоким тепловыделением, такие как SoC с ядрами CPU и GPU, могут быть размещены в нижней части стека или на более высоком уровне интеграции, обеспечивая гибкость стекирования, невиданную в предыдущих конфигурациях PoP.

Реализации могут применяться в таких приложениях, как, но не только, низкое энергопотребление и/или архитектура памяти с широкой полосой пропускания ввода-вывода. Реализации могут обеспечить короткий канал с удвоенной скоростью передачи данных (DDR) для соседних функциональных блоков (например, SoC, чипсетов и т. д.) за счет использования RDL и прямого крепления чипов. Реализации могут быть особенно применимы для мобильных приложений, которые требуют низкого энергопотребления DDR при целевой производительности, включая высокую скорость и широкую полосу пропускания ввода-вывода.

Преимущества описанных методов многочисленны. Использование памяти с более высокой пропускной способностью приведет к улучшению производительности. Гибкость размещения компонентов сокращает расстояние между подключенными активными и пассивными устройствами, либо снижая энергию, необходимую для связи между ними, либо уменьшая паразитные эффекты, которые могут вызывать нежелательную потерю мощности или деградацию динамической производительности. Наиболее заметными задачами, которые выиграют, являются игры и обработка изображений, которые часто требуют большого объема данных за короткие промежутки времени.

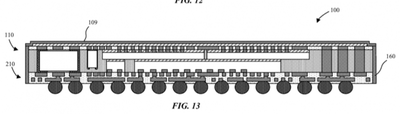

Связь с Apple Watch

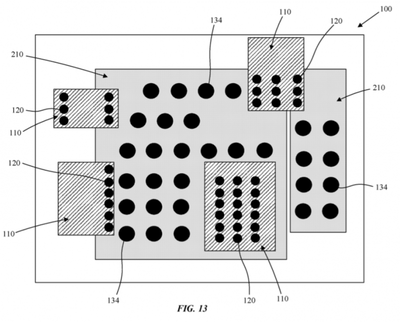

Эти улучшения были бы применимы ко всем мобильным устройствам Apple, но в нескольких патентных заявках конкретно упоминаются методы объединения нескольких компонентов в Системе в Корпусе (SiP), как это видно в текущих Apple Watch. Описанные ниже методы являются улучшением существующих решений SiP, используемых в Apple Watch, поскольку они представляют собой истинные элементы 3D-стекирования, реализованные как через TSV, так и через сквозные оксидные переходные отверстия (TOV).

В одном аспекте реализации описывают разделение на кристаллах системы на кристалле (SoC) и/или разделение кристаллов в структуре SiP (например, 3D-корпус памяти), в которой IP-ядра, такие как CPU, GPU, IO, DRAM, SRAM, кеш, ESD, управление питанием и интегрированные пассивные компоненты, могут свободно разделяться по всему корпусу, одновременно снижая общую высоту корпуса по оси Z.

Кроме того, в патенте подробно описываются шаги TSV и TOV, что предполагает, что сохранение малой высоты корпуса позволяет создавать переходные отверстия очень малого диаметра, причем TOV образуют ряды межсоединений размеров меньше, чем даже TSV. Также обсуждается влияние TSV на активные части кристалла, включая снижение производительности транзисторов, и уменьшенные шаги помогают смягчить это.

Включены РЧ-трансиверы и активные устройства на подложках, которые в настоящее время не используются в мобильных устройствах Apple, указывая на то, что все типы активных и пассивных компонентов, обнаруженных в продуктах Apple Watch, могут быть размещены в предлагаемом SiP.

Временная шкала

Корпуса с компонентами, соединенными по технологиям 2.5D и 3D, существуют в потребительских устройствах уже несколько лет, но большинство описанных выше методов еще не дебютировали в мобильных устройствах. Описанные шаги приведут к увеличению производственной сложности, и, вероятно, в результате пострадают стоимость и пропускная способность.

Из-за проблем с затратами и выходом годных изделий основным кандидатом на первое применение этих методов будет устройство с высокой маржой и низким объемом производства. В то время как iPhone является продуктом Apple с самой высокой маржой среди мобильных продуктов, это также самая крупносерийная категория с огромным первоначальным спросом на каждое поколение. iPad Pro является хорошим кандидатом из-за своего низкого объема производства и классификации как высокопроизводительное устройство. Включение частоты обновления 120 Гц — это то, что выиграет от увеличения пропускной способности памяти, в частности.

Фокус многих из этих патентов, по-видимому, сосредоточен на методах SiP, используемых во внутренностях Apple Watch. Apple Watch — это устройство с меньшим объемом производства, и оно выиграет, поскольку его внутренние компоненты чрезвычайно чувствительны к размеру корпуса, учитывая важность его форм-фактора и размера аккумулятора. Можно ожидать, что некоторые из описанных методов будут включены уже в следующем поколении Apple Watch, и более прогрессивно в будущих ревизиях.